### **FEATURES**

### PRODUCT APPEARANCE

- Fully compatible with the ISO 11898 standard

- > Thermally protected

- > High CMTI: 100 kV/μs

- > Transmit Data (TXD) dominant time-out function

- ➤ Bus fault protection of -40V to +40V

- > Input levels compatible with 3.3 V and 5 V devices

- ➤ Low loop delay: 150ns (Typical) 210ns (Max)

- > At least 110 nodes can be connected

- ➤ High speed (up to 1 MBaud)

- ➤ High system level EMC performance

- ightharpoonup packages: DUB8 V<sub>ISO</sub>=2500 V<sub>RMS</sub> SOPW16, V<sub>ISO</sub>=5000 V<sub>RMS</sub>

Provide green and environmentally friendly lead-free package

### DESCRIPTION

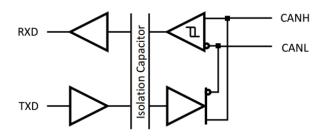

SIT1050ISO is a capacitively isolated CAN transponder, which complies with the technical specifications of the ISO11898 standard. It contains multiple logic input and output buffers separated by silicon dioxide (SiO2) insulation barriers. The device provides differential transmit capability to the bus and differential receive capability to the CAN controller.

| PARAMETER                             | SYMBOL             | CONDITION               | MIN.     | MAX.     | UNIT         |

|---------------------------------------|--------------------|-------------------------|----------|----------|--------------|

| WB DUB8 Withstand isolation voltage   | $V_{\rm ISO}$      |                         | 250      | 2500 typ |              |

| WB SOPW16 Withstand isolation voltage | $ m V_{ISO}$       |                         | 5000 typ |          | $ m V_{RMS}$ |

| Common-Mode Transients                | CMTI               |                         | 50       | 100      | kV/μs        |

| Supply voltage                        | $V_{cc}$           |                         | 4.5      | 5.5      | V            |

| Maximum transmission rate             | 1/t <sub>bit</sub> | Non-return to zero code | 1        |          | Mbaud        |

| CANH/CANL input or output voltage     | $V_{can}$          |                         | -40      | +40      | V            |

| Bus differential voltage              | $V_{ m diff}$      |                         | 1.5      | 3.0      | V            |

| High-level input voltage              | $V_{\mathrm{IH}}$  | TXD                     | 2        | 5.25     | V            |

| Low-level input voltage               | $V_{IL}$           | TXD                     | 0        | 0.8      | V            |

| High-level output current             | Іон                | Driver                  | -70      |          | mA           |

| PARAMETER                 | SYMBOL            | CONDITION | MIN. | MAX. | UNIT |

|---------------------------|-------------------|-----------|------|------|------|

| High-level output current | $I_{\mathrm{OH}}$ | Receiver  | -4   |      | mA   |

| Low-level output current  | $I_{OL}$          | Driver    |      | 70   | mA   |

|                           |                   | Receiver  |      | 4    | mA   |

| Virtual junction          | $T_{i}$           |           | -40  | 150  | °C   |

| temperature               | ,                 |           |      |      |      |

Function diagram

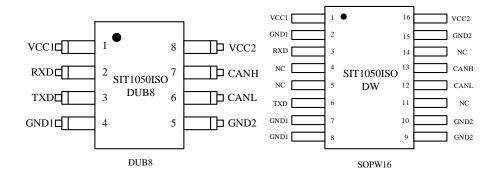

# PIN CONFIGURATION

# PIN DESCRIPTION

#### **DUB8** pin description

| PIN | SYMBOL    | DESCRIPTION                                             |

|-----|-----------|---------------------------------------------------------|

| 1   | $V_{CC1}$ | Power Supply for Logic Side, range 3.0V~5.5V.           |

| 2   | RXD       | Receive data output.                                    |

| 3   | TXD       | Transmit data input.                                    |

| 4   | GND1      | Ground 1, the ground reference for Isolator Logic Side. |

| 5   | GND2      | Ground 2, the ground reference for Isolator Bus Side.   |

| 6   | CANL      | LOW-level CAN bus line.                                 |

| PIN | SYMBOL        | DESCRIPTION                                 |

|-----|---------------|---------------------------------------------|

| 7   | CANH          | HIGH-level CAN bus line.                    |

| 8   | $V_{\rm CC2}$ | Power supply for Bus Side, range 4.5V~5.5V. |

### SOPW16 pin description

| PIN | SYMBOL    | DESCRIPTION                                             |

|-----|-----------|---------------------------------------------------------|

| 1   | VCC1      | Power Supply for Logic Side, range 3.0V~5.5V.           |

| 2   | GND1      | Ground 1, the ground reference for Isolator Logic Side. |

| 3   | RXD       | Receive data output.                                    |

| 4   | NC        | No Connection.                                          |

| 5   | NC        | No Connection.                                          |

| 6   | TXD       | Transmit data input.                                    |

| 7   | GND1      | Ground 1, the ground reference for Isolator Logic Side. |

| 8   | GND1      | Ground 1, the ground reference for Isolator Logic Side. |

| 9   | GND2      | Ground 2, the ground reference for Isolator Bus Side.   |

| 10  | GND2      | Ground 2, the ground reference for Isolator Bus Side.   |

| 11  | NC        | Not connect.                                            |

| 12  | CANL      | LOW-level CAN bus line.                                 |

| 13  | CANH      | HIGH-level CAN bus line.                                |

| 14  | NC        | Not connect.                                            |

| 15  | GND2      | Ground 2, the ground reference for Isolator Bus Side.   |

| 16  | $V_{CC2}$ | Power supply for Bus Side, range 4.5V~5.5V.             |

# LIMITING VALUES

| PARAMETER                                      | SYMBOL             | VALUE                      | UNIT |

|------------------------------------------------|--------------------|----------------------------|------|

| Supply voltage                                 | $V_{CC1}, V_{CC2}$ | -0.5~+6.5                  | V    |

| TXD voltage                                    | TXD                | -0.5~V <sub>CC1</sub> +0.5 | V    |

| Voltage range at any bus terminal              | CANL, CANH         | -40~40                     | V    |

| Transient voltage on pins CANH, CANL see Fig.7 | $ m V_{tr}$        | -200~+200                  | V    |

| Storage temperature                            | $T_{ m stg}$       | -40~150                    | °C   |

| Virtual junction temperature                   | $T_{\rm j}$        | -40~150                    | °C   |

| Welding temperature range                      |                    | 300                        | °C   |

The maximum limit parameters mean that exceeding these values may cause irreversible damage to the device. Under these conditions, it is not conducive to the normal operation of the device. The continuous operation of the device at the maximum allowable rating may affect the reliability of the device. The reference point for all voltages is ground.

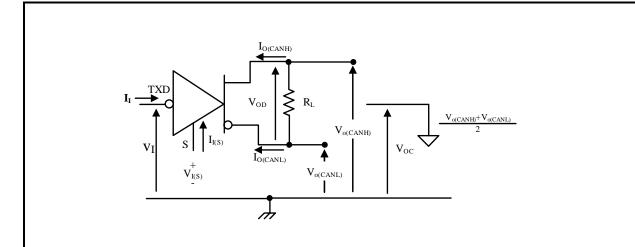

### DRIVER ELECTRICAL CHARACTERISTICS

| PARAMETER                                | SYMBOL                  | CONDITION                                                                   | MIN.         | TYP. | MAX.        | UNIT |

|------------------------------------------|-------------------------|-----------------------------------------------------------------------------|--------------|------|-------------|------|

| CANH dominant output voltage             | $V_{\mathrm{OH}(D)}$    | VI=0V, RL=60Ω,                                                              | 2.9          | 3.4  | 4.5         | V    |

| CANL dominant output voltage             | $V_{\text{OL}(D)}$      | Fig.1, Fig.2                                                                | 0.8          |      | 1.5         | V    |

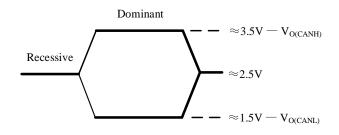

| Bus recessive output voltage             | $V_{O(R)}$              | VI=3V, RL=60Ω,<br><u>Fig.1</u> , <u>Fig.2</u>                               | 2            | 2.5  | 3           | V    |

| Bus dominant differential output voltage | V <sub>OD(D)</sub>      | VI=0V, RL=60Ω,<br><u>Fig.1</u> , <u>Fig.2</u>                               | 1.5          |      | 3           | V    |

| Bus recessive differential output        | $V_{\mathrm{OD(R)}}$    | VI=3V,<br><u>Fig.1</u> , <u>Fig.2</u>                                       | -0.012       |      | 0.012       | V    |

| voltage                                  |                         | VI=3V, NO LOAD                                                              | -0.5         |      | 0.05        | V    |

| Transmitter dominant voltage symmetry    | $V_{\text{dom(TX)sym}}$ | $V_{\text{dom(TX)sym}} = V_{\text{CC}} - V_{\text{CANH}} - V_{\text{CANL}}$ | -400         |      | 400         | mV   |

| Transmitter voltage symmetry             | $V_{TXsym}$             | $V_{TXsym} = V_{CANH} + V_{CANL}$                                           | $0.9 V_{CC}$ |      | $1.1V_{CC}$ | V    |

| PARAMETER                               | SYMBOL             | CONDITION                                                                                                     | MIN. | ТҮР. | MAX. | UNIT  |

|-----------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| Common-mode output voltage              | V <sub>OC</sub>    | Fig.8                                                                                                         | 2    | 2.5  | 3    | V     |

| Peak-to-peak Common-mode output voltage | $\triangle V_{OC}$ |                                                                                                               |      | 30   |      | mV    |

| Short-circuit output current            |                    | CANH=-12V,<br>CANL=open,<br>Fig.11                                                                            | -105 | -72  |      | mA    |

|                                         | $I_{OS}$           | CANH=12V,<br>CANL=open,<br>Fig.11                                                                             |      | 0.36 | 1    | mA    |

|                                         |                    | CANL=-12V,<br>CANH=open,<br><u>Fig.11</u>                                                                     | -1   | 0.5  |      | mA    |

|                                         |                    | CANL=12V,<br>CANH=open,<br><u>Fig.11</u>                                                                      |      | 71   | 105  | mA    |

| Recessive output current                | $I_{O(R)}$         | -27V <canh<32v<br>0<vcc<5.25v< td=""><td>-2.0</td><td></td><td>2.5</td><td>mA</td></vcc<5.25v<></canh<32v<br> | -2.0 |      | 2.5  | mA    |

| Common-Mode<br>Transients               | CMTI               | <u>Fig.12</u>                                                                                                 | ±50  |      | ±100 | kV/μs |

$(V_{CC1} = V_{CC2} = 5V \pm 10\%, Temp = T_{MIN} \sim T_{MAX}, typical in \ V_{CC1} = V_{CC2} = +5V, Temp = 25^{\circ}C.)$

# DRIVER SWITCHING CHARACTERISTICS

| PARAMETER                                              | SYMBOL       | CONDITION     | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------------|--------------|---------------|------|------|------|------|

| Propagation delay time,<br>low-to-high-level<br>output | tPLH         | Fig.4         | 31   | 65   | 120  | ns   |

| Propagation delay time,<br>low-to-high-level<br>output | tPHL         |               | 25   | 45   | 90   | ns   |

| Differential output signal rise time                   | tr           |               |      | 25   |      | ns   |

| Differential output signal fall time                   | tf           |               |      | 50   |      | ns   |

| Bus dominant time-out time                             | $t_{ m dom}$ | <u>Fig.10</u> | 300  | 450  | 700  | μs   |

$\overline{(V_{CC1}=V_{CC2}=5V\pm10\%, Temp=T_{MIN}\sim T_{MAX}, typical in V_{CC1}=V_{CC2}=+5V, Temp=25^{\circ}C.)}$

## RECEIVER ELECTRICAL CHARACTERISTICS

| PARAMETER                                   | SYMBOL              | CONDITION                           | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------|---------------------|-------------------------------------|------|------|------|------|

| Positive-going input threshold voltage      | $V_{\mathrm{IT}^+}$ | Fig.5                               |      | 800  | 900  | mV   |

| Negative-going input threshold voltage      | V <sub>IT</sub> -   |                                     | 500  | 650  |      | mV   |

| Hysteresis voltage<br>(VIT+ – VIT–)         | $ m V_{HYS}$        |                                     | 100  | 125  |      | mV   |

| High-level output voltage                   | $ m V_{OH}$         | IO=-2mA, <u>Fig.6</u>               | 4    | 4.6  |      | V    |

| Low-level output voltage                    | $V_{OL}$            | IO=2mA, <u>Fig.6</u>                |      | 0.2  | 0.4  | V    |

| Power-off bus input current                 | I <sub>(OFF)</sub>  | CANH or<br>CANL=5V,<br>Other pin=0V |      | 165  | 250  | μА   |

| Input capacitance to ground, (CANH or CANL) | $C_{\mathrm{I}}$    |                                     |      | 13   |      | pF   |

| Differential input capacitance              | $C_{ID}$            |                                     |      | 5    |      | pF   |

| Input resistance,<br>(CANH or CANL)         | $R_{\rm IN}$        | TVD_2V                              | 15   | 30   | 40   | kΩ   |

| Differential input resistance               | $R_{ m ID}$         | TXD=3V                              | 30   |      | 80   | kΩ   |

| Input resistance matching                   | RI <sub>match</sub> | CANH=CANL                           | -3%  |      | 3%   |      |

| The range of common-mode voltage            | $ m V_{COM}$        |                                     | -12  |      | 12   | V    |

$\overline{(V_{CC1}=V_{CC2}=5V\pm10\%, Temp=T_{MIN}\sim T_{MAX}, typical in V_{CC1}=V_{CC2}=+5V, Temp=25^{\circ}C.)}$

# RECEIVER SWITCHING CHARACTERISTICS

| PARAMETER                                 | SYMBOL | CONDITION    | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------------|--------|--------------|------|------|------|------|

| Propagation delay time, low-to-high-level | tPLH   | <u>Fig.6</u> | 60   | 100  | 130  | ns   |

| output                                    |        |              |      |      |      |      |

| PARAMETER                                              | SYMBOL | CONDITION | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------------|--------|-----------|------|------|------|------|

| Propagation delay time,<br>low-to-high-level<br>output | tPHL   |           | 45   | 70   | 105  | ns   |

| RXD signal rise time                                   | tr     |           |      | 8    |      | ns   |

| RXD signal fall time                                   | tf     |           |      | 8    |      | ns   |

$\overline{(V_{CC1}=V_{CC2}=5V\pm10\%, Temp=T_{MIN}\sim T_{MAX}, typical in V_{CC1}=V_{CC2}=+5V, Temp=25^{\circ}C.)}$

# DEVICE SWITCHING CHARACTERISTICS

| PARAMETER                                                            | SYMBOL                | CONDITION    | MIN. | TYP. | MAX. | UNIT |

|----------------------------------------------------------------------|-----------------------|--------------|------|------|------|------|

| Loop delay1, driver input to receiver output, Recessive to Dominant  | t <sub>d(LOOP1)</sub> | <u>Fig.9</u> | 112  |      | 210  | ns   |

| Loop delay 2, driver input to receiver output, Dominant to Recessive | t <sub>d(LOOP2)</sub> |              | 112  |      | 210  | ns   |

$\overline{(V_{CC1}=V_{CC2}=5V\pm10\%, Temp=T_{MIN}\sim T_{MAX}, typical in V_{CC1}=V_{CC2}=+5V, Temp=25^{\circ}C.)}$

# LOGIC SIDE ELECTRICAL CHARACTERISTICS

| PARAMETER                | SYMBOL           | CONDITION                         | MIN.     | ТҮР. | MAX. | UNIT |

|--------------------------|------------------|-----------------------------------|----------|------|------|------|

| High level input voltage | $ m V_{IH}$      | TXD pin                           | 2        |      |      | V    |

| Low level input voltage  | $ m V_{IL}$      | TXD pin                           |          |      | 0.8  | V    |

| High level input current | $ m I_{IH}$      | TXD pin                           |          |      | 10   | μΑ   |

| Low level input current  | ${ m I}_{ m IL}$ | TXD pin                           | -10      |      |      | μΑ   |

| Output Voltage High      | $ m V_{OH}$      | I <sub>OH</sub> =-4mA, RXD<br>pin | VDD1-0.4 |      |      | V    |

| Output Voltage Low       | $V_{OL}$         | I <sub>OL</sub> =4mA, RXD<br>pin  |          |      | 0.4  | V    |

| Input Capacitance        | $C_{\rm IN}$     | TXD pin                           |          | 2    |      | pF   |

### OVER TEMPERATURE PROTECTION

| PARAMETER         | SYMBOL | CONDITION | MIN. | TYP. | MAX. | UNIT |

|-------------------|--------|-----------|------|------|------|------|

| Shutdown junction | T:/- A |           |      | 160  |      | °C   |

| temperature       | Tj(sd) |           |      | 100  |      |      |

## SUPPLY CURRENT

| PARAMETER                       | SYMBOL                       | CONDITION                                     | MIN. | ТҮР. | MAX. | UNIT |

|---------------------------------|------------------------------|-----------------------------------------------|------|------|------|------|

| V. C l                          | ī                            | $V_I = 0V$ or $V_{CC1}$ ,<br>$V_{CC1} = 3.3V$ |      | 1.8  | 2.8  | mA   |

| V <sub>CC1</sub> Supply current | $I_{CC1}$                    | $V_I = 0V$ or $V_{CC1}$ , $V_{CC1} = 5V$      |      | 2.3  | 3.6  | mA   |

| V <sub>CC2</sub> Supply current | ply current I <sub>CC2</sub> | $V_{I}\!\!=\!\!0V$ LOAD= $60\Omega$           |      | 50   | 70   | mA   |

|                                 |                              | V <sub>I</sub> =VCC                           |      | 6    | 10   | mA   |

$(V_{CC1} = V_{CC2} = 5V \pm 10\%, Temp = T_{MIN} \sim T_{MAX}, typical in \ V_{CC1} = V_{CC2} = +5V, Temp = 25^{\circ}C.)$

## FUNCTION TABLE

#### Table1.CAN TRANSCEIVER TRUTH TABLE

|        | DRIVER  |      |           |                            | CEIVER |           |

|--------|---------|------|-----------|----------------------------|--------|-----------|

| INPUTS | OUTPUTS |      |           | CANH CANH                  | DVD    | DUG GEAGE |

| TXD    | CANH    | CANL | BUS STATE | CANH- CANL                 | RXD    | BUS STATE |

| L      | Н       | L    | Dominate  | V <sub>ID</sub> ≥0.9V      | L      | Dominate  |

| Н      | Z       | Z    | Recessive | $0.5V < V_{ID} < 0.9V$     | ?      | ?         |

| Open   | Z       | Z    | Recessive | $V_{ID} \le 0.5 \text{ V}$ | Н      | Recessive |

| X      | Z       | Z    | Recessive | Open                       | Н      | Recessive |

<sup>(1)</sup> H=high level; L=low level; X=irrelevant.

**Table 2. DRIVER FUNCTION TABLE**

| INPUTS         | OUT      | Dug State |           |

|----------------|----------|-----------|-----------|

| <b>TXD</b> (1) | CANH (1) | CANL (1)  | Bus State |

| L              | Н        | L         | Dominate  |

| Н              | Z        | Z         | Recessive |

<sup>(1)</sup> H=high level; L=low level; X=irrelevant; Z=high impedance.

#### **Table 3. RECEIVER FUNCTION TABLE**

| V <sub>ID</sub> =CANH-CANL | V <sub>ID</sub> =CANH-CANL | Bus State | Bus State |

|----------------------------|----------------------------|-----------|-----------|

|                            | V <sub>ID</sub> ≥0.9V      | Dominate  | Dominate  |

| Normal or Silent           | $0.5 < V_{ID} < 0.9V$      | ?         | ?         |

|                            | $V_{ID} \leq 0.5V$         | Recessive | Recessive |

|                            | Open (VID≈0V)              | OPEN      | Recessive |

<sup>(1)</sup> H=high-level; L=low-level; ?=uncertain.

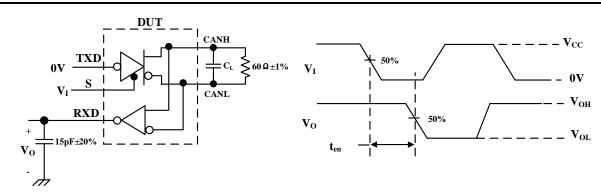

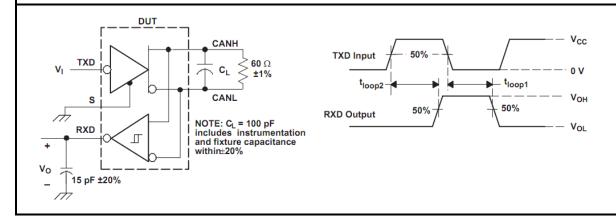

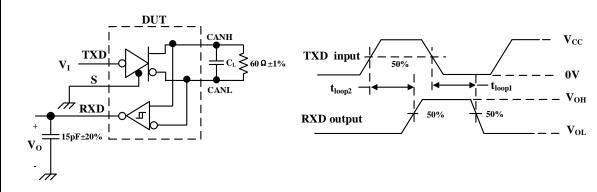

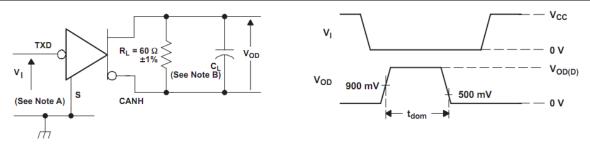

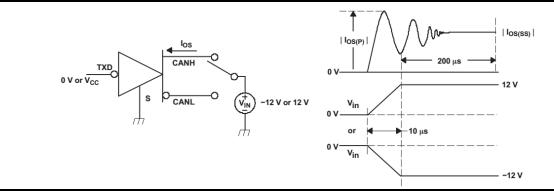

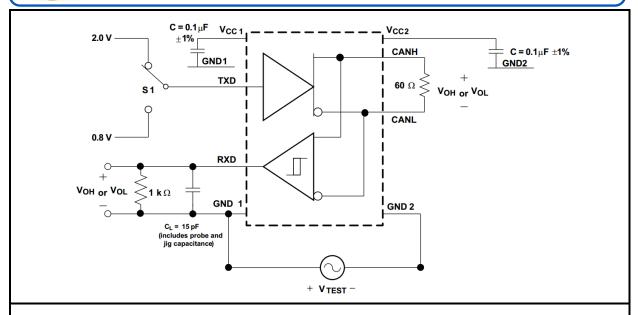

TEST CIRCUIT

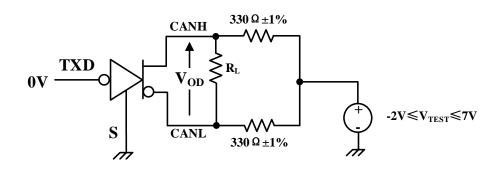

Fig.1 Driver Voltage, Current, and Test Definition

Fig.2 Bus Logic State Voltage Definition

Fig.3 Driver Vod Test Circuit

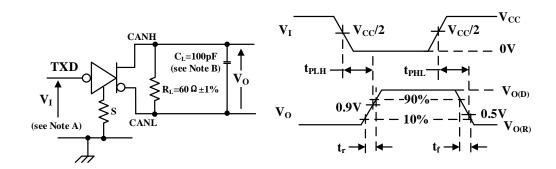

- A. The input pulse is supplied by a generator having the following characteristics: PRR $\le$ 125 kHz, 50% duty,  $t_r \le$ 6 ns,  $t_t \le$ 8 ns,  $t_t \le$ 8 ns,  $t_t \le$ 8 ns,  $t_t \le$ 9 ns,

- B.  $C_L$  includes instrumentation and fixture capacitance within  $\pm 20\%$

#### Fig.4 Driver Test Circuit and Waveform

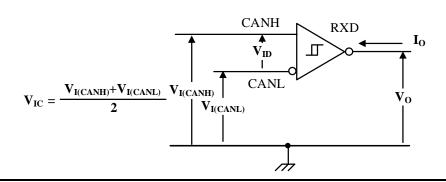

Fig.5 Receiver Voltage and Current Definition

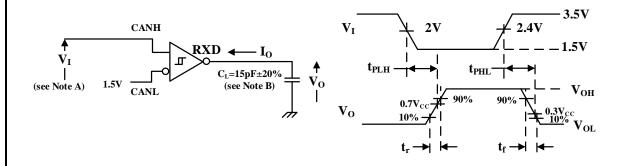

- A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  125 kHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6ns,  $Z_O =$  50 O

- B.  $C_L$  includes instrumentation and fixture capacitance within  $\pm 20\%$ .

#### Fig.6 Receiver Test Circuit and Waveform

NOTE:  $C_L=100$ pF includes instrumentation and fixture capacitance with  $\pm 20\%$ ;

All  $V_L$  input pulses are supplied by a generator having the following characteristics:  $t_r \le 6$  ns,  $t_f \le 6$ ns, Pulse Repetition Rate (PRR)=25kHz, 50% duty cycle.

#### Fig.7 $t_{EN}$ Test Circuit and Waveform

A. All  $V_I$  input pulses are from 0 V to VCC and supplied by a generator having the following characteristics:  $t_r$  or  $t_f \le 6$  ns. Pulse Repetition Rate (PRR) = 125 kHz, 50% duty cycle.

Fig.8 Peak-to-Peak Common Mode Output Voltage Test and Waveform

NOTE:  $C_L$ =100pF includes instrumentation and fixture capacitance within  $\pm 20\%$ .

#### Fig.9 t<sub>(LOOP)</sub> Test Circuit and Waveform

- A. The input pulse is supplied by a generator having the following characteristics:  $t_r \le 6$  ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ ns,  $t_f \le 6$ n

- B.  $C_L$  includes instrumentation and fixture capacitance with  $\pm 20\%$

#### Fig.10 Dominant Time-Out Test Circuit and Waveform

Fig.11 Driver Short-Circuit Current Test Circuit and Waveform

Fig.12 Common-Mode Transient Immunity Test Circuit

### ADDITIONAL DESCRIPTION

#### 1 Sketch

SIT1050ISO is an interface chip with isolation function for CAN protocol controller and physical bus, and can be applied to the fields of in-vehicle, industrial control etc. It is primarily intended for high-speed applications, up to 1 MBaud, in passenger cars. The device provides differential transmit capability to the bus and differential receive capability to the CAN controller, and fully compatible with the ISO 11898 standard.

Provide wide body SOPW16 package, isolation withstand voltage 5000V<sub>RMS</sub>.

Provide wide-body DUB8 package, isolation with stand voltage  $2500V_{RMS}$ , Common-Mode Transients up to  $100kV/\mu s$ .

#### 2 Current protection

A current-limiting circuit protects the transmitter output stage from damage caused by accidental short-circuit to either positive or negative supply voltage, although power dissipation increases during this fault condition.

#### 3 Over temperature protection

The output drivers are protected against over-temperature conditions. If the virtual junction temperature exceeds the shutdown junction temperature  $T_{j(sd)}$ , the output drivers will be disabled until the virtual junction temperature becomes lower than  $T_{j(sd)}$  and TXD becomes recessive again. By including the TXD condition, the occurrence of output driver oscillation due to temperature drifts is avoided.

#### 4 TXD dominant time-out function

A 'TXD dominant time-out' timer circuit prevents the bus lines from being driven to a permanent dominant state (blocking all network communication) if pin TXD is forced permanently LOW by a hardware and/or software application failure. The timer is triggered by a negative edge on pin TXD.

If the duration of the LOW level on pin TXD exceeds the internal timer value ( $t_{dom}$ ), the transmitter is disabled, driving the bus lines into a recessive state. The timer is reset by a positive edge on pin TXD.

#### 5 Operating mode

SIT1050ISO works in high-speed mode, which is the default working mode.

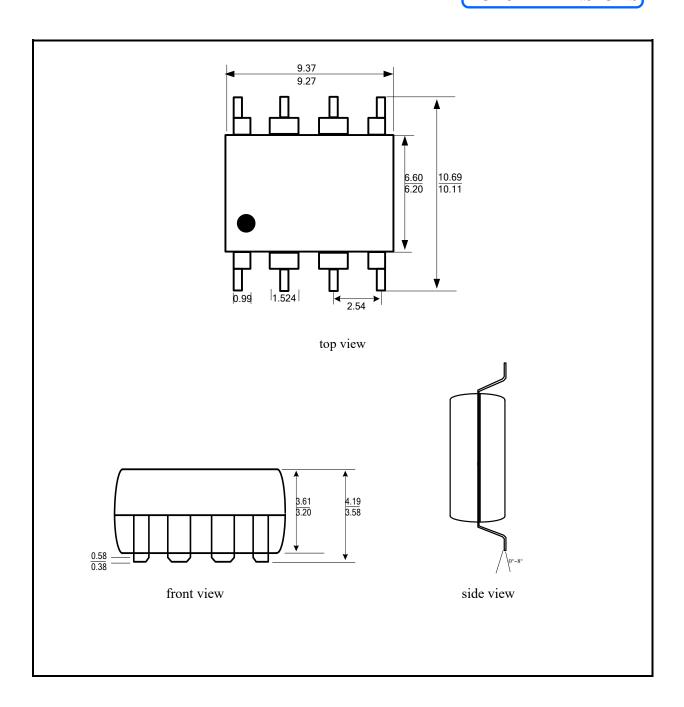

# **DUB8 DIMENSIONS**

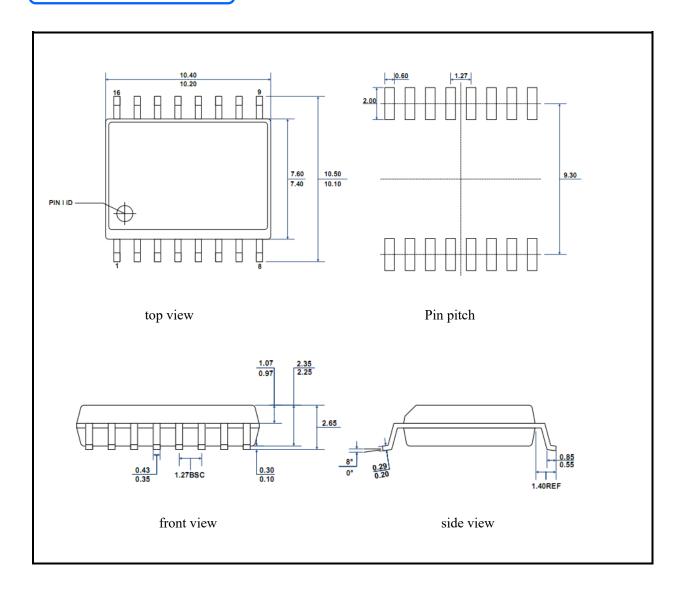

## SOPW16 DIMENSIONS

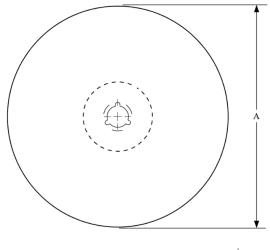

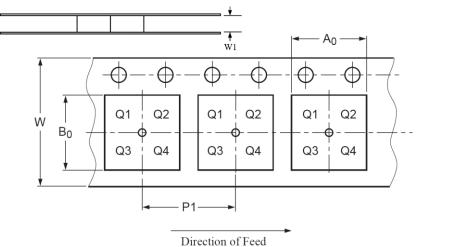

## TAPE AND REEL INFORMATION

| 4.0 | Dimension designed to accommodate the   |

|-----|-----------------------------------------|

| A0  | component width                         |

| В0  | Dimension designed to accommodate the   |

| В   | component length                        |

| K0  | Dimension designed to accommodate the   |

| KU  | component thickness                     |

| W   | Overall width of the carrier tape       |

| P1  | Pitch between successive cavity centers |

$K_0$

PIN1 is in quadrant 1

| Package<br>Type | Reel<br>Diameter<br>A (mm) | Tape width W1 (mm)   | A0<br>(mm) | B0 (mm)    | K0<br>(mm) | P1 (mm)    | W<br>(mm)                             |

|-----------------|----------------------------|----------------------|------------|------------|------------|------------|---------------------------------------|

| DUB8            | 330±2.0                    | $24.4^{+2.0}_{-0.0}$ | 11.00±0.10 | 9.60±0.10  | 4.40±0.10  | 16.00      | 24.00 <sup>+0.3</sup> <sub>-0.1</sub> |

| SOPW16          | 330±2.0                    | $16.4^{+2.0}_{-0.0}$ | 10.75±0.10 | 10.70±0.10 | 2.80±0.10  | 12.00±0.10 | 16.00±0.20                            |

# ORDERING INFORMATION

| TYPE NUMBER    | PACKAGE | PACKING       |

|----------------|---------|---------------|

| SIT1050ISODUB8 | DUB8    | Tape and reel |

| SIT1050ISODW   | SOPW16  | Tape and reel |

DUB8 is packed with 800 pieces/disc in braided packaging. SOPW16 is packed with 1000 pieces/disc in braided packaging.

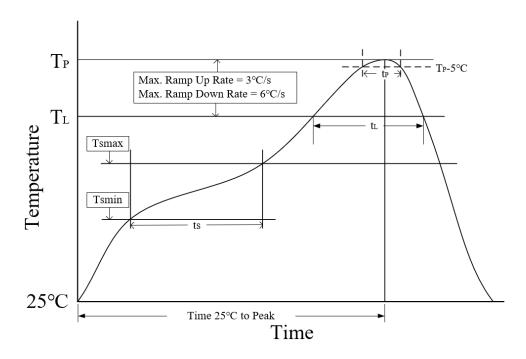

## REFLOW SOLDERING

| Parameter                                            | Lead-free soldering conditions |

|------------------------------------------------------|--------------------------------|

| Ave ramp up rate (T <sub>L</sub> to T <sub>P</sub> ) | 3°C/second max                 |

| Preheat time ts                                      | 60-120 seconds                 |

| $(T_{smin}=150$ °C to $T_{smax}=200$ °C)             | 00-120 seconds                 |

| Melting time $t_L(T_L=217^{\circ}C)$                 | 60-150 seconds                 |

| Peak temp T <sub>P</sub>                             | 260-265°C                      |

| 5°C below peak temperature t <sub>P</sub>            | 30 seconds                     |

| Ave cooling rate (T <sub>P</sub> to T <sub>L</sub> ) | 6°C/second max                 |

| Normal temperature 25°C to peak temperature          | 8 minutes max                  |

| T <sub>P</sub> time                                  | o minutes max                  |

#### Important statement

SIT reserves the right to change the above-mentioned information without prior notice.

# VERSION HISTORY

| Version number | Data sheet status                                                                                                                                                                                                                                                                                                    | Revision date |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| V1.0           | Initial version.                                                                                                                                                                                                                                                                                                     | March 2022    |

| V1.1           | Adjusted the format.                                                                                                                                                                                                                                                                                                 | November 2020 |

| V1.2           | Updated the maximum value of low loop delay; Updated DUB8 schematic.                                                                                                                                                                                                                                                 | February 2021 |

| V1.3           | Added V <sub>IH</sub> , V <sub>IL</sub> , I <sub>OH</sub> and I <sub>OL</sub> ; Added "logical side electrical characteristics"; Deleted the information of SOPW8; Added "tape and reel information"; Updated ordering information; Added "reflow soldering"; Added "important statement"; Added "revision history". | December 2022 |